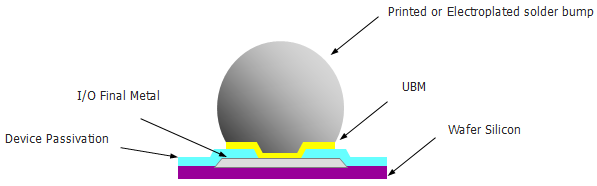

Our Standard Flip Chip process, formerly known as the Flex-on-Cap (or FoC) process, was originally developed in the mid-1960’s by Delco for use in the automotive industry. Today, the process has unsurpassed industry track record with 40 years and millions of bumped wafers behind it. This is the process to use when you need to place small bumps (less than 130μm in height) directly on the die I/O.

Bump on I/O Flip chip

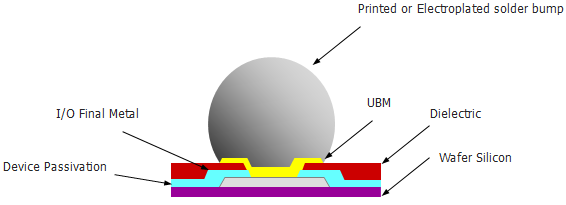

Bump on I/O Flip chip Repassivated Flip chip

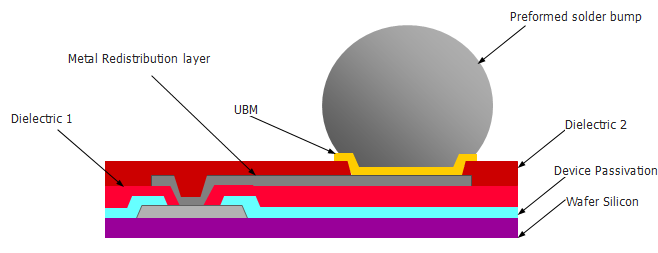

Repassivated Flip chip RDL Flip chip

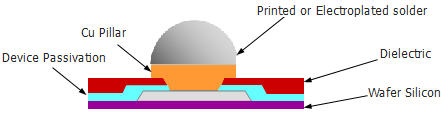

RDL Flip chip Repassivated Cu Pillar

Repassivated Cu Pillar